一、指令周期的概念:

CPU从主存中取出并执行一条指令的时间被称为指令周期。

一个指令周期包含若干机器周期(机器周期也称为CPU周期);

一个机器周期包含若干时钟周期(时钟周期又称为节拍或者T周期或者CPU时钟周期,是CPU操作的最基本单位)。

每个指令周期内的机器周期数量可以不同,每个机器周期内的时钟周期数量也可以不同。

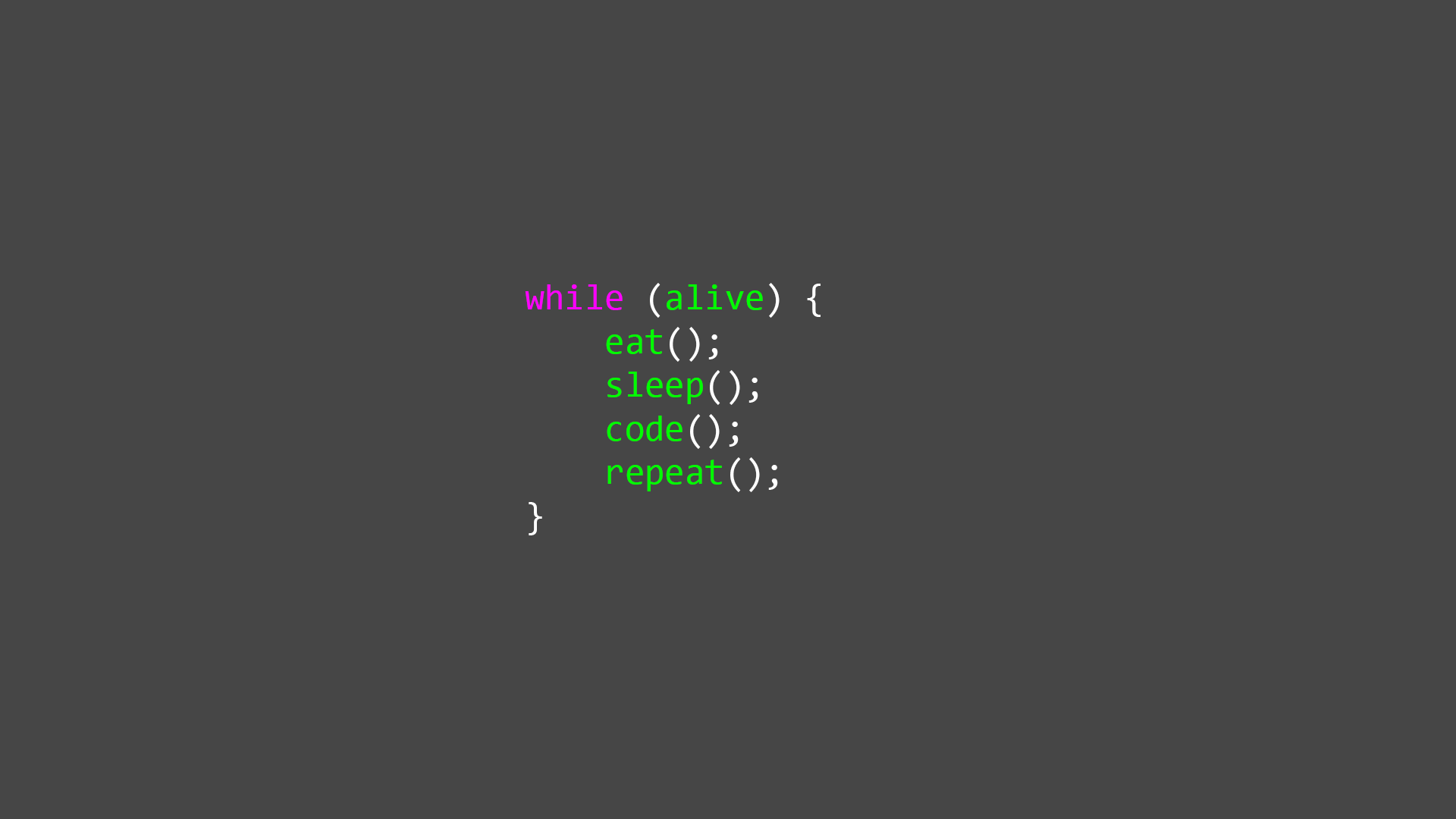

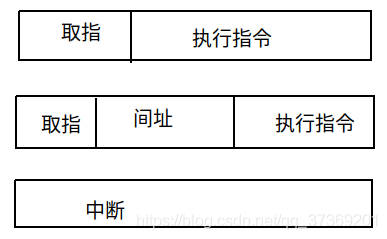

不同的指令的指令周期可能不同,如:

1.注:分析指令所需时间足够短因此归于取出指令的阶段

2.注:一般情况下每执行一条指令结束后都会进入中断周期 3.注:间址周期CPU进行间接取址

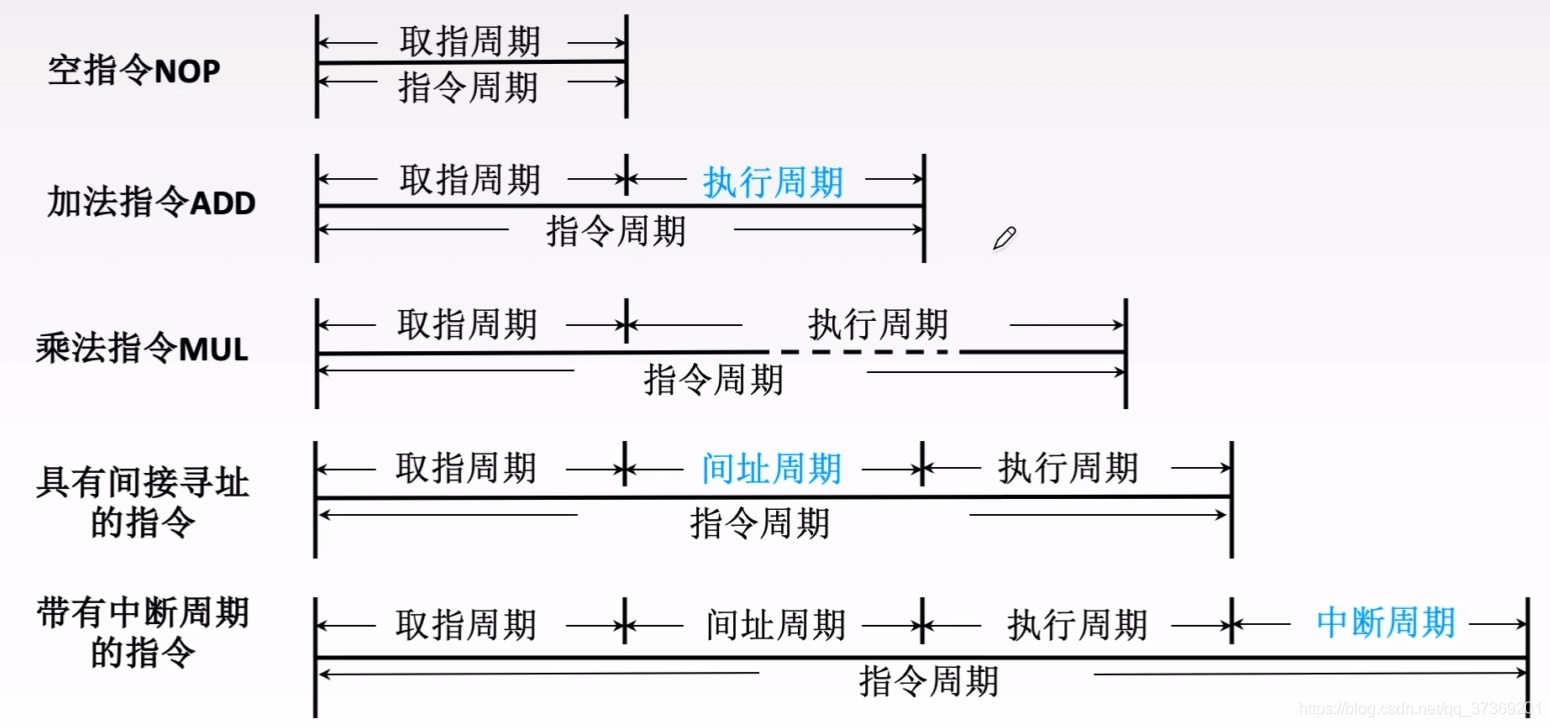

机器周期又可分为定长机器周期和不定长机器周期,其实质是一个机器周期内包含的时钟周期数量不同,如下图,一个方波代表一个时钟周期,不同长度的机器周期包含不同数量的波(下图画红色代表一个时钟周期)。

1.2上述指令中涉及到的四种周期:

取指周期:从主存中取出一条指令。 间址周期:把形式地址转化成有效地地址,即取操作数的有效地址。 执行周期:执行指令对应的操作。 中断周期:在非关中断的状态下,每条指令结束时都会留下中断周期以检测中断信号。

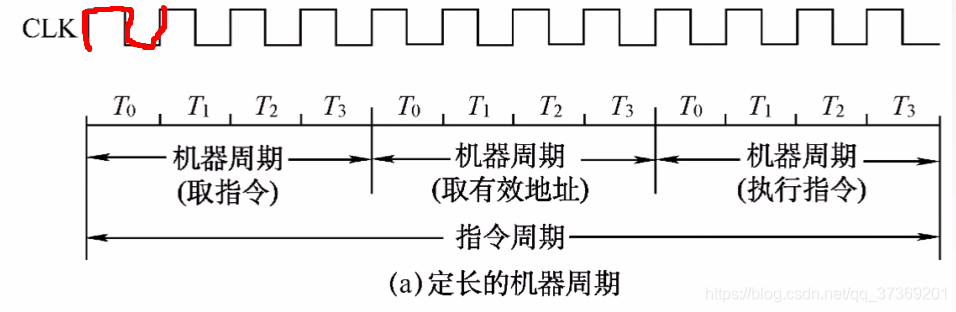

Q:如何判断CPU处于哪个周期:

A:设置四个触发器,每个触发器中存放一个0或1,1表示处于当前周期,0表示不在当前周期,控制单元CU控制触发器中是0还是1。

A:设置四个触发器,每个触发器中存放一个0或1,1表示处于当前周期,0表示不在当前周期,控制单元CU控制触发器中是0还是1。

二、指令周期的数据流向:

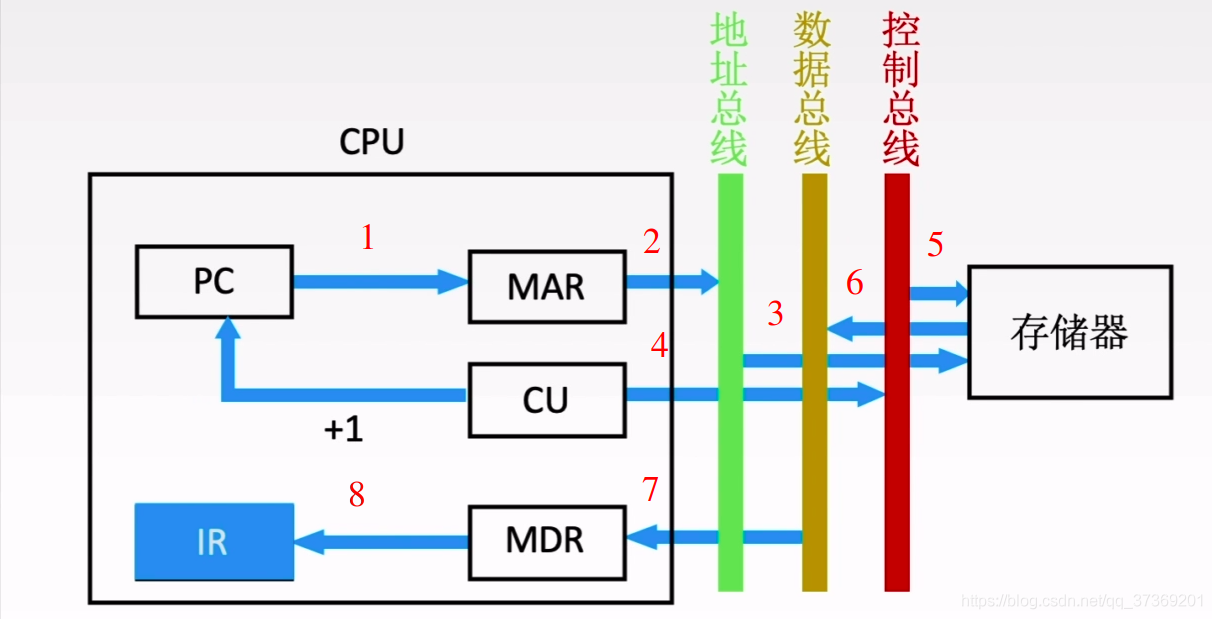

2.1 取指周期

1).PC中存放了下一条指令存放地址,因此把PC中保存的地址发送到MAR,记作(PC)->MAR; 2).控制单元CU(Control Unit)通过控制总线发出控制信号给主存储器,发出的是读(R)信号,记作1->R; 3).MAR所指主存地址存放的数据经数据总线发送到MDR,记作M(MAR)->MDR; 4).CU发出控制信号,形成下一条指令的地址,记作(PC)+1->PC。 数据流向的图解为:

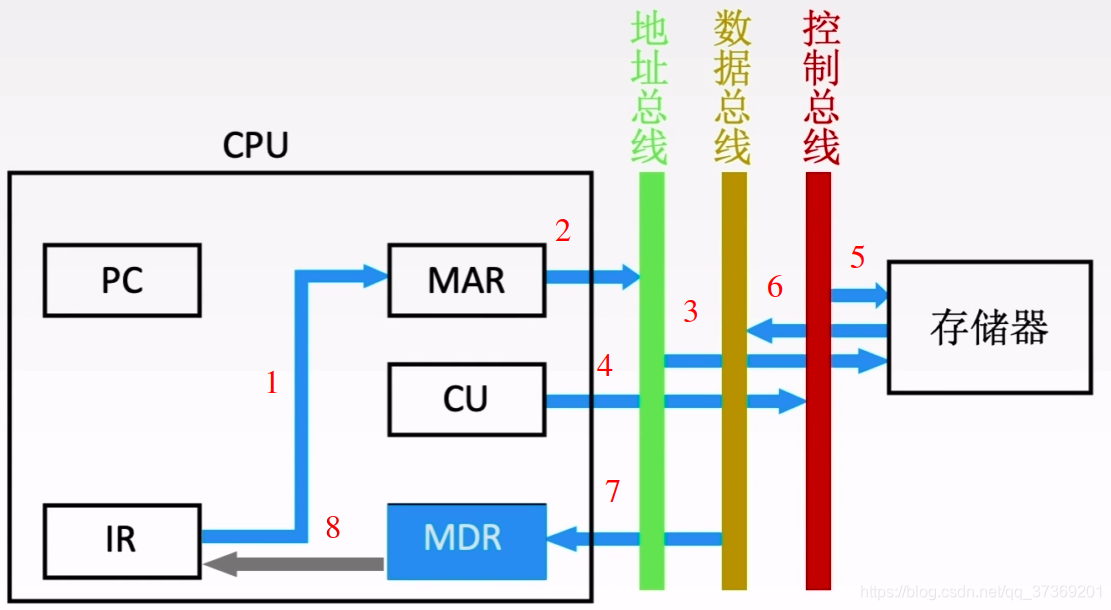

2.2 间址周期

1).IR中指令的地址码送入MAR,此时MDR中也还存留着送入IR时的数据,因此也可以直接通过MAR送入MDR,记作Ad(IR)->MAR或者Ad(MDR)->MAR;

2).CU通过通知总线发出读(R)控制信号给主存储器,记作1->R;

3).MAR所指主存地址存放的数据经数据总线发送到MDR,记作M(MAR)->MDR;

4).把有效地址送入指令的地址码字段,拼出新的指令,记作(MDR)->Ad(IR)。这一步可以不操作,只属于部分类型的CPU。

数据流向的图解为:

2.3 执行周期

执行周期的指令各种各样

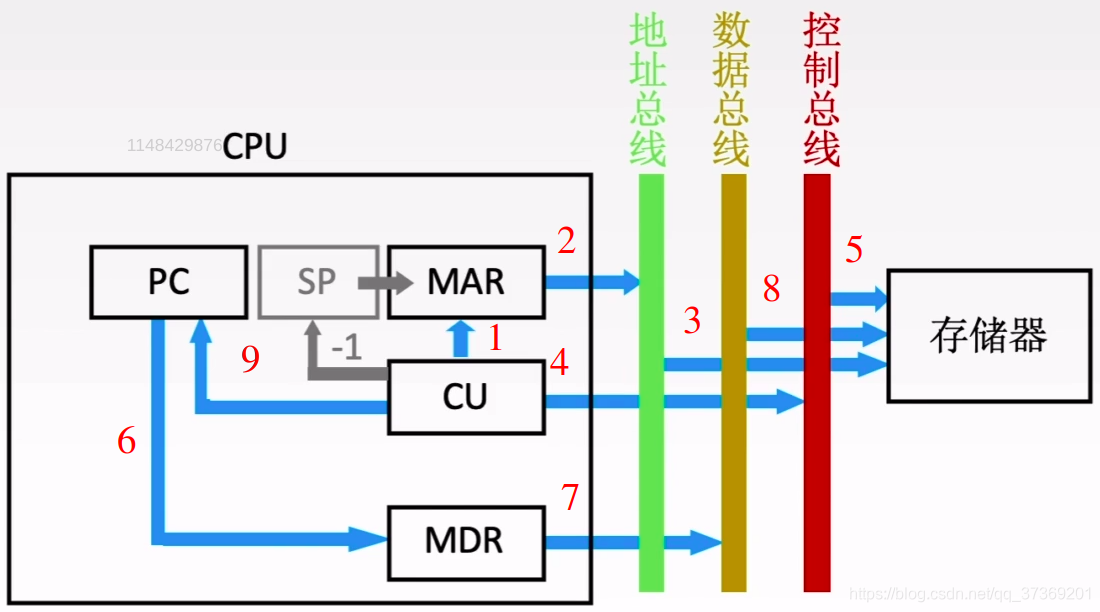

2.4 中断周期

1).CU控制栈顶地址SP-1,把修改后的地址送入MAR,记作(SP)-1->SP,(SP)->MAR,实质是把进程断点存储到主存的存储单元; 2).CU通过控制总线发出写控制信号到主存,记作1->W; 3).断点信息的内容送入MDR,记作(PC)->MDR; 4).CU控制将中断服务的程序入口地址送入PC,记作向量地址->PC。 数据流向的图解为:

1.注:W和R分别指的是写和读操作,主存设置两个接口W和R,W通高电平为1则写操作,R同理。 2.注:类似M(MAR)->MDR这样的写法,M(MAR)意为MAR中存储的内容。 3.注:间址周期标红部分,前面文章有介绍到指令只由操作码和地址码构成,地址码部分可以存放指令所在地址也可以存放其他操作数存放地址。 4.注:实际上计算机中堆栈寄存器的栈顶指针,是由上到下即由高到低,因此中断周期有“CU控制栈顶地址SP-1”这一操作,意为栈顶指针向下移动一指向新位置。

三、指令执行方案:

3.1单指令周期

指令之间串行执行,每条指令的执行周期长度相同。指令周期的长度取决于执行过程中最长一条指令的执行时间。

指令之间串行执行,每条指令的执行周期长度相同。指令周期的长度取决于执行过程中最长一条指令的执行时间。

3.2多指令周期

与单指令周期不同,多指令周期中每个指令的执行周期可以长短不一。多指令周期的指令也是串行执行。

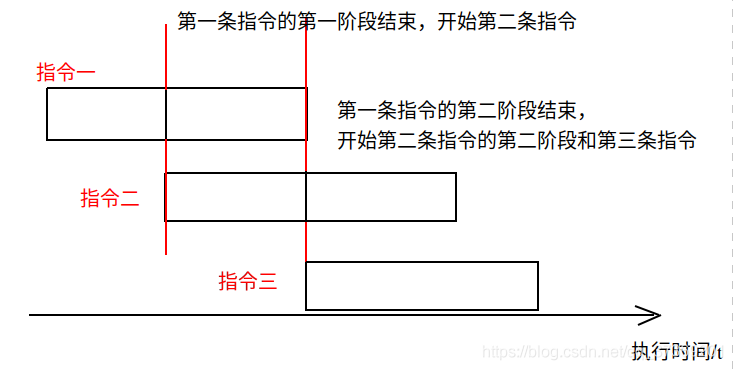

3.3流水线方案

当每条指令使用到的硬件不同时,可以采用流水线方案。

这里留坑等待后续补充。。。。