在学习时序逻辑的时候,我们明白寄存器赋值总有一拍的延迟但是有的时候仿真的时候会发现会没有延迟,比如下面这段代码对应的modelsim仿真。

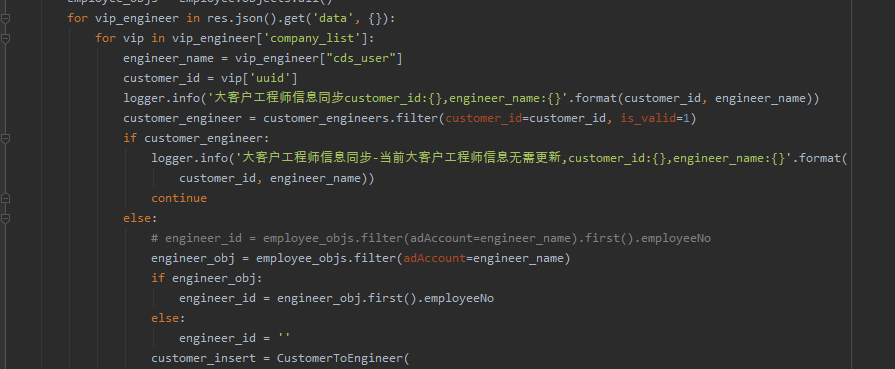

源代码代码如下:

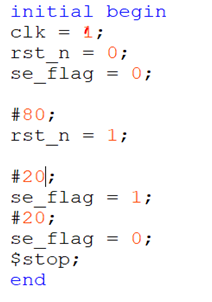

测试激励如下:

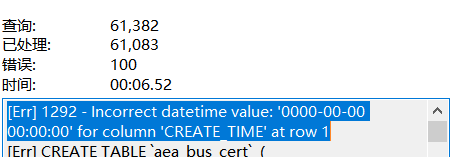

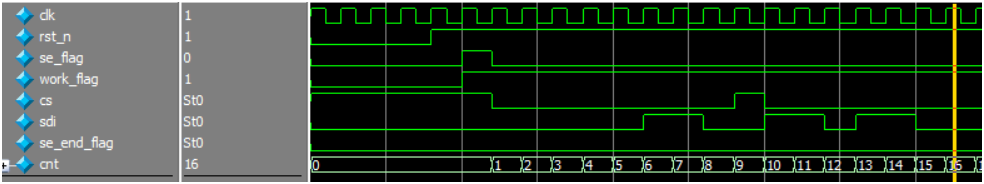

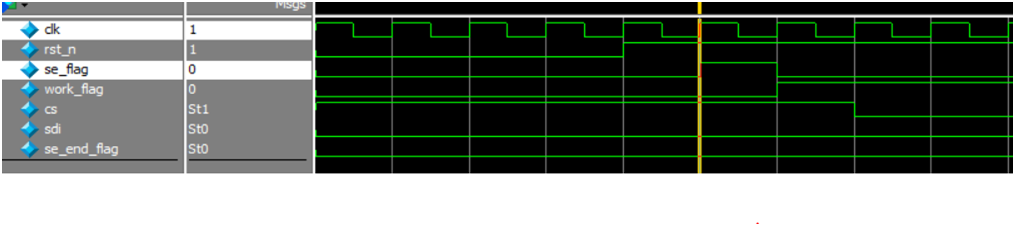

仿真截图如下:

2.从仿真截图可以看出work_flag与se_flag几乎是同时拉高的,那么造成这个现象的原因是什么呢?

对代码的理解应该是这样的:如果时钟上升沿到来与se_flag == 1,那么在下一个时钟延到来时会让work_flag ==1,而在我们手动给se_flag激励的时候modelsim会认为在时钟上升沿之前se_flag已经等于1了,虽然这个在波形中看不出来,但是我们需要明白。

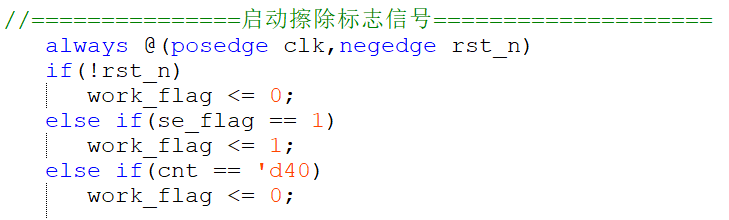

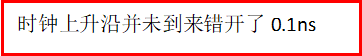

3:如何解决这种问题呢?其实办法很简单,就是我们在激励中尽量se_flag与时钟上升沿错开,即滞后一点再给激励,具体如下。

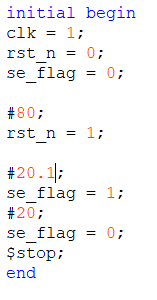

仿真截图如下:

仿真截图如下:

4.这样在时钟上升沿到来时,se_flag还是0并未是1,便可以看到我们希望的理想结果。