Intel SGX 技术是一种新的基于硬件的可信计算技术。该技术通过CPU的安全扩展,对用户空间运行环境(enclave)提供机密性和完整性保护。即使是攻击者获得OS,hypervisor,BIOS 和SMM 等权限,也无法直接攻击enclave。因此,攻击者不得不通过侧信道的攻击方法来间接获取数据(比如隐私数据,加密密钥等等)。得益于enclave 的强安全假设和工作模型,攻击者有大量的侧信道攻击面可以选择,比如页表,cache,DRAM 等等。这个工作就是对侧信道攻击面进行一个全面的总结,并讨论一些可能的防御和检测方法。

1 引言

当我们不能够完全相信某个计算平台(比如公有云和可能被攻破的操作系统)的时候,建立个可信的运行环境(TEE)是一个非常重要的安全要求。近些年研究人员提出了很多TEE 系统用于保护应用程序,使其能够抵御来自操作系统的攻击[5, 6, 12]。为了防御更强的攻击,比如来自hypervisor 或SMM 的攻击,Intel在2013 年HASP会议的workshop正式推出了Intel SGX。该技术通过CPU 的安全扩展,对用户空间运行环境(enclave)提供基于硬件(CPU)的保护。即使是攻击者获得了OS,hypervisor,BIOS,SMM 等权限,也无法直接读取或者修改enclave 的内容。

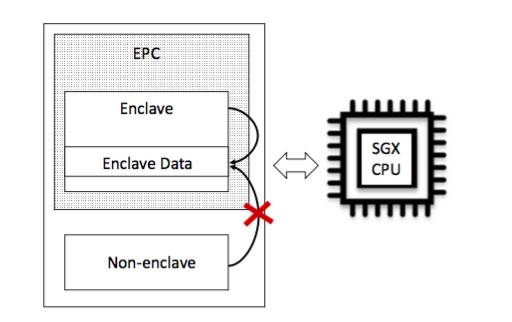

Enclave 的运行环境有大量的资源和外面non-enclave 公用,比如cache,页表,DRAM 和分支预测器等,这就给攻击者提供了丰富的侧信道攻击面。而且,不可信的操作系统还仍然负责管理系统的资源,比如页表,内存,中断,进程调度等等,这就进一步方便攻击者减小侧信道攻击过程中的噪音,从而提高侧信道攻击的成功率。

本文主要调研和总结目前已有的侧信道攻击。根据攻击面的不同,我们将从页表,TLB,cache,DRAM 和分支预测器等几个面进行侧信道攻击的介绍。SGX 的侧信道攻击十分难以防御。目前还没有一种防御策略可以防御以上所有攻击。本文最后对可能的侧信道防御攻击方法进行简要的总结,希望读者能够在某些方面受到启发。

2 SGX 背景介绍

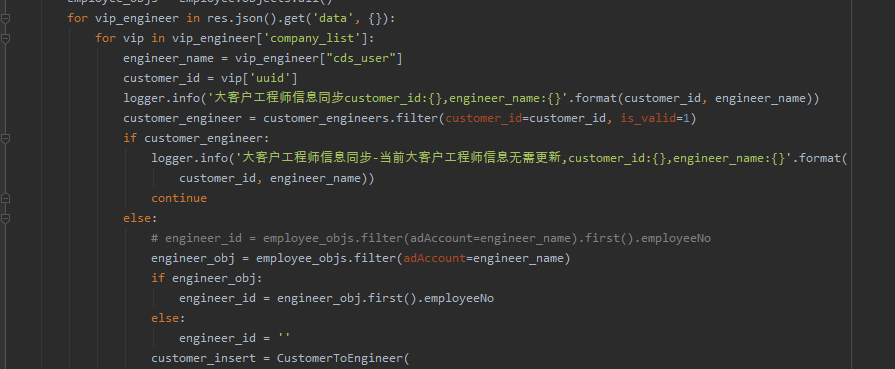

Intel SGX 是一种基于硬件的TEE系统。该功能已经集成在Intel Sky-Lake 系列。区别以往的TEE 系统有着较大的可信计算基(TCB),SGX 的可信计算基非常小,仅仅包含CPU 和enclave 本身。任何的特权软件,比如OS,hypervisor,BIOS,SMM 等都不包含在可信计算基内。Enclave有SGX 硬件专门预留的EPC(Enclave Page Cache)内存。EPC是PRM(processor reserved memory)的子集,并被系统软件按照4KB粒度进行分页管理。每一个EPC 页面只能分配给一个enclave。CPU 阻止任何non-enclave 去访问PRM,任何non-enclave 的访问都会导致一个失败的事务(aborted transaction)。在目前SkyLake 的处理器上面,失败的写操作被忽略,失败的读操作直接返回一个全1的值。

每个enclave 的程序指定一段ELRANGE(Enclave Linear AddressRange)的虚拟空间供自身运行。页表负责把虚拟地址映射为EPC所在的物理地址。页表的工作原理和以往的页表一样,比如会进行权限的检测、会设置access bit和dirty bit等等。Enclave 和non-enclave 可以通过EENTER 和EEXIT 来主动切换工作模式。Enclave 运行时可能会被中断或者异常打断,这个时候enclave 会通过AEX(Asynchronous EnclaveExit)机制退出,切换到non-enclave工作模式。在模式切换过程中,运行状态会保存到SSA结构体(State Save Area )里面,同时清除TLB以保证enclave 的安全。

图1: Intel SGX 内存分布和隔离机制。Enclave 跑在EPC 上面。Enclave的数据仅可以被enclave 自己访问,任何外界代码的访问都会被拒绝。

3 SGX 侧信道攻击

本章重点介绍SGX 的侧信道攻击。首先介绍SGX侧信道攻击的威胁模型,然后概括介绍侧信道的攻击面。最后,根据攻击面的不同,再分别介绍一下目前已经发表的侧信道攻击。

3.1 威胁模型

侧信道攻击主要目标是攻击enclave数据的机密性(confidentiality)。攻击者来自non-enclave 部分,包括应用程序和系统软件。系统软件包括OS,hypervisor,SMM,BIOS 等特权级软件。

侧信道攻击一般假设攻击者知道enclave 初始化时候的代码和数据,并且知道内存布局。内存布局包括虚拟地址,物理地址以及他们之间的映射关系。有些侧信道攻击假设攻击者知道enclave 的输?数据,并且可以反复触发enclave,进行多次观察记录。侧信道攻击还假设攻击者知道运行enclave 平台的硬件配置、特性和性能,比如CPU,TLB,cache,DRAM,页表,中断以及异常等各种系统底层机制。

3.2 侧信道的攻击面

enclave 和non-enclave共享大量的系统资源,这就给侧信道攻击留下了非常大的攻击面。经过对现有资料的总结和系统结构的分析,我们把SGX的攻击总结在图2里面。

图2: Intel SGX 侧信道的攻击面。

如图2所示,enclave 的运行过程中会用到:

1. CPU 内部结构。比如pipeline,branch prediction Buffer(BPB)等等。这些结构不能够直接访问,但是如果可以间接利用[16],仍然可能泄露enclave的控制流或数据流。

2. TLB。TLB 有包括iTLB,dTLB 和L2 TLB。如果HyperThreading打开,两个逻辑核共享一个物理核,这个时候会大大增加侧信道的可能。

3. Cache。Cache 包括L1 instruction cache,L1 data cache,L2cache 和L3 cache(又叫LLC cache)。

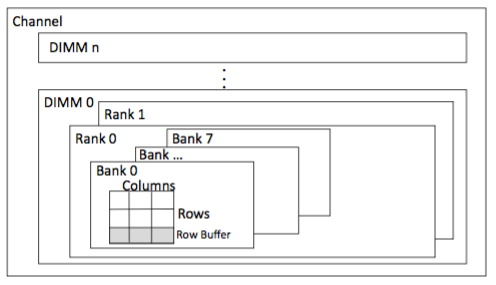

4. DRAM。DRAM 包含channels,DIMMs,ranks,banks。每个banks又包含rows、columns 和row buffer。

5. Pagetable(页表)。页表可以通过权限控制来触发缺页异常,也可以通过页表的状态位来表明CPU 的某些操作。对于不同的攻击面,攻击者需要了解具体的细节和工作原理。其中比较重要的参考的文档就是Intel 的手册[14, 13]。目前SGX 已经部署在SkyLake 的机器上面。因此我们需要对SkyLake 的一些硬件和性能细节重点掌握。文档[2]对SkyLake i7-6700 的一些CPU 细节和性能做了一个比较全面的介绍和测量。

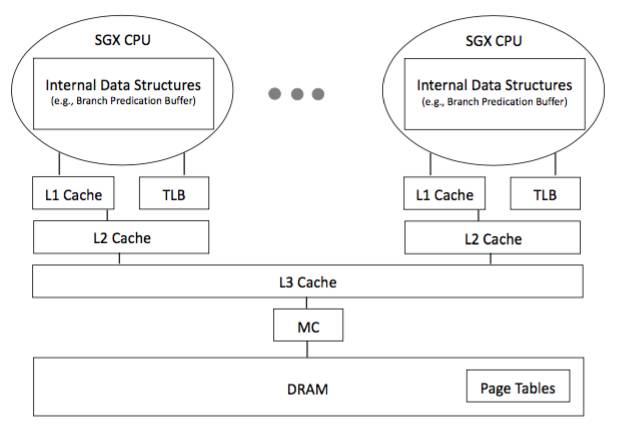

目前,文章[28]发现了Intel文档的一处描述和实际实验有冲突,在这里需要重点说明一下。具体来讲Intel 文档[13] 指出SkyLake机器,在打开hyperthreading之后的TLB的配置信息如图3。然而,根据文章[28]的实验,这个Intel 文档对于TLB partition 的描述是不准确的。实验结果表明,iTLB 是fixed partition,其他(dTLB 和L2 TLB)都是dynamicpartition。本文尚未实验验证上述实验结果。如果大家用到这部分知识,还需独立实验验证。

图3: SkyLake 的TLB 配置。注意这里的partition 信息可能不准确。

3.3 侧信道攻击

侧信道攻击主要手段是通过攻击面获取数据,推导获得控制流和数据流信息,最终获取被enclave的代码和数据的信息,比如加密密钥,隐私数据等等。我们这里不一一列举具体的工作,而是试图从攻击面的角度,全面的介绍侧信道攻击。本章节下面的内容,就从典型的攻击面,包括页表,TLB,cache,DRAM 以及CPU 内部结构,描述目前已知的侧信道攻击。

3.3.1 基于页表的攻击

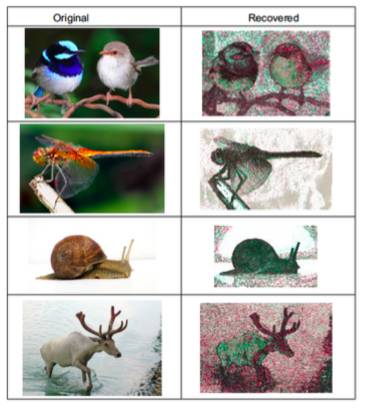

最早的SGX 侧信道攻击就是基于页表的攻击[29, 27]。这类利用页表对enclave 页面的访问控制权,设置enclave 页面为不可访问。这个时候任何访问都会触发缺页异常,从而能够区分enclave 访问了哪些页面。按照时间顺序把这些信息组合,就能够反推出enclave 的某些状态和保护的数据。该类典型的攻击包括controlled-channel attack [29] 和pigeonholeattack [27]。这类攻击的缺点就是精度只能达到页粒度,无法区分更细粒度的信息。但是在某些场景下,这类攻击已经能够获得大量有用信息。例如图4所示,这类基于页表的侧信道攻击可以获得libjpeg 处理的图片信息.经过还原,基本上达到人眼识别的程度。pigeonhole 攻击也展示了大量对现有的安全库的攻击,如图5所示。

图4: Controlled-channel 攻击对libjpeg 的攻击效果。

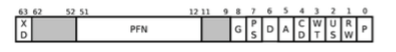

后来,基于页表的攻击有了新的变种。这些侧信道攻击主要利用页表的状态位[28]。如图6所示,一个页表项有很多位,有些是用来做访问控制,比如P, RW, US, XD,有些则标识状态,比如D(dirty bit)和A(accessbit)。如果A bit 被设置,则表明该页表项指向的页面已经被访问;如果Dbit被设置,则表明该页表项指向的页面发生了写操作。通过监控观察这些状态位,攻击者就可以获取和controlled-channel/pigeonhole 攻击类似的信息。

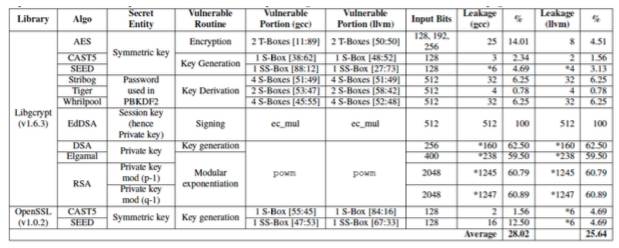

图5: Pigeonhole 攻击对安全库的攻击效果。

图6: 典型的页表项的格式(x64 系统)。其中D 标识dirty,A 标识Access。

3.3.2 基于TLB 的攻击

目前还没有完全基于TLB 的攻击,但是已经出现TLB 作为辅助手段的侧信道攻击,我们会在混合侧信道攻击的章节3.3.6里面介绍。关于TLB的两点重要信息,我们需要了解,希望对提出新的基于TLB 的侧信道攻击和防御有所帮助。

1. TLB 的层次结构。目前SkyLake 的机器,分为L1 和L2 两层。不同层次出现的TLB miss 的时间代价不同。

2. TLB 对代码和数据的区分。L1 区分代码(iTLB)和数据(dTLB)。两者直接有cache coherence 的保证。L2 不区分代码和数据。

3.3.3 基于Cache 的攻击

传统侧信道有很多基于cache 的攻击[19, 30, 17, 10, 11]。在SGX的环境里面,这些侧信道技术仍然适用,而且可以做的更好。原因在于,在SGX 环境里面攻击者可以控制整个系统的资源。因此,攻击者可以有针对性地调度资源,减小侧信道的噪音,增加侧信道的成功率。降低噪音的策略大体可以有以下几种[8, 21, 1, 25]:

1. Core Isolation(核隔离)。这个方法的主要目标就是让enclave 独自占有一个核(不允许其他程序运行在该核上面)。

2. Cache Isolation(缓存隔离)。尽量使用L1 或者L2 级别的cache 进行侧信道攻击。L3 的cache 被所有的核共用,会引入不必要的噪音。

3. Uninterupted Execution(不间断运行)。也就是不触发或尽量少触发AEX,因为AEX 和后续的ISR(interrupt sevice rountine) 都会使用cache,从而引入不必要噪音。少触发AEX 就是要使用中断绑定(interrupt affinity)和将时钟频率。不触发AEX 基本上就是让系统软件(比如OS)屏蔽所有中断。

除了降低噪音,攻击者还可以提高攻击的精度,大体策略有:

1. 高精度时钟。可以采用APIC 提供的高精度时钟和硬件TSC。

2. 放大时间差异。比如攻击者可以配置侧信道攻击代码所在的CPU 以最高频率运行,而对enclave 所在的CPU 进行降频处理。

基于cache 的侧信道攻击可以进行细粒度的监控。最小粒度可以做到一个cache line,即64个字节。由于粒度更小,基于cache 的侧信道可以比基于页表的侧信道(以及后面介绍的基于DRAM 的侧信道)获得更多的信息。

3.3.4 基于DRAM 的攻击

在讲解基于DRAM 的侧信道之前,我们首先了解一些DRAM 的基本知识。DRAM 一般由channel,DIMM, rank, bank 等部分构成,如图7所示。每个bank 又有columns 和rows 组成。每个bank里面还有一个row buffer 用来缓存最近访问过的一个row。在访问DRAM 的时候,如果访问地址已经被缓存在row buffer 当中(情况A),就直接从buffer 里面读取,否则需要把访问地址对应的整个row 都加载到row buffer 当中(情况B)。当然,如果row buffer 之前缓存了其他row 的内容,还需要先换出row buffer 的内容再加载新的row(情况C)。A、B、C 对应的三种情况,访问速度依次递减(情况A 最快,情况C 最慢)。这样,通过时间上的差异,攻击者就可以了解当前访问的内存地址是否在row buffer 里面,以及是否有被换出。文章[25] 在侧信道攻击过程中用到了基于DRAM 的侧信道信息。另外文章[23] 介绍了更多基于DRAM 的攻击细节,不过该文章不是在SGX 环境下的攻击。

图7: 典型的DRAM 的格式。DRAM 根据物理地址选择channel,DIMM,rank, bank, 以及row 和column。

基于DRAM 的侧信道攻击有一些不足[28]。第一,enclave 使用的内存通常都在缓存里面,只有少部分需要从DRAM 里面去取。第二,DRAM的精度不够。例如,一个页面(4KB) 通常分布在4 个DRAM row 上面。这样,基于DRAM 的侧信道攻击的精度就是1KB。仅仅比基于页表的侧信道攻击好一些,远远不及基于cache 的侧信道攻击的精度。第三,DRAM里面存在很难避免的噪音干扰,因为一个DRAM row 被很多页面使用,同时同一个bank 不同row的数据读取也会对时间测量造成干扰,使得误报时常发生。

3.3.5 基于CPU 内部结构的攻击

CPU 内部有大量的结构是在enclave 和non-enclave 之间共用的。这就给侧信道攻击提供了大量的攻击面素材。比如文章[16] 里面提出使用BPB(Branch Prediction Buffer)来实现侧信道攻击。具体来讲,在enclave 和non-enclave 切换的时候,BPB ??存留的跳转预测记录并没有被清除。这样使得non-enclave 可以构造一个程序,测试这些跳转预测记录。如果预测成功,则执行时间较短。反之,如果预测失败,则执行时间较长。通过时间上的差异,攻击者就可以推测enclave 之前运行的跳转分支,进而获得enclave 运行的控制流图。通过控制流图,攻击者又可以进一步推测隐私数据,比如加密密钥等。这个攻击的强大之处在于他几乎可以还原整个控制流。这样细粒度的信息使得该攻击可以泄露很多信息。文章也进行了大量实验,充分展示了这个攻击的强大。实验表明,这个攻击可以泄露字符串信息,RSA 私钥以及网络数据等等。

目前对以CPU 内部结构为攻击面的工作才刚刚开始,仅仅有一个工作发表。相信通过进一步研究,还会有其他的攻击面被陆续发掘。

从设计上来讲,SGX 可以避免这类侧信道攻击。具体来讲,在enclave到non-enclave 的切换过程中,CPU 清除这些共?的内部结构体。这样,non-enclave 就不会得到任何残留的记录。但在具体实现的时候,还要注意一些细节,比如清除的时间也必须是稳定不变的。如果enclave 运行的差异会导致清除操作的时间差异,攻击者很可能据此推导出enclave 的某些运行状态。

3.3.6 混合侧信道攻击

混合侧信道攻击是(1)同时采集多个侧信道攻击面的信息,或(2)通过多个攻击面共同作用放大差异增加准确度。比较典型的做法包括:

1. TLB 和页表混合攻击。比如TLB miss 的时候会加载页表,这个时候CPU 会设置页表的Access bit。文章[28] 就在hyperthreading 的情况下,触发大量的TLB miss,再通过观察页表的A bit 进行侧信道攻击。

2. Cache 和DRAM 混合攻击。基于DRAM 的攻击只能精确到row(一个row 通常8KB)的粒度。为了增强这类攻击效果,文章[28] 提出了这个cache-DRAM 攻击来增加空间精度,把精度提高到了一个cache line(64B)。

除了结合两个攻击面的侧信道攻击,还可以采用多个攻击面相结合的侧信道攻击。这类混合攻击我还没有在SGX 的环境下面看到相关工作。不过之前CCS‘16 的文章[9],使用了三个攻击面(i.e., TLB、页表和cache)的混合。我相信类似的攻击也可以在SGX 的环境下使用。

3.4 未来可能的侧信道攻击

未来新的侧信道攻击可能来自两个方面。第一就是发掘新的混合侧信道攻击。前面列出的经典的混合侧信道攻击,他们往往使用两种攻击面信息。因此,我们可以考虑多个攻击面结合的侧信道攻击。以往的混合侧信道攻击往往专注于内存管理和地址转换等方面,新的侧信道攻击可以结合其他方面的信息,进行一些新的尝试。

Enclave 所有和non-enclave 共享的资源都可能成为潜在的侧信道攻击面。因此,发掘新的侧信道攻击的第二个途径就是发现新的共享资源,比如未被发掘的CPU 内部共享结构。这些新的的共享资源可能来自一些新的硬件特性,比如Intel PT, Intel TSX, Intel MPX, Intel CAT 等等。

4 可能的防御方法

目前已经有很多文章给出了防御SGX 侧信道的方案,有些只是大体的思路,有些则已经有成型的设计和实现。我们在这里主要介绍防御的思路和方法,不涉及设计和实现的细节。首先,我们把这些方法涉及的层次,分为源码级别,系统级别和硬件级别。

4.1 源码层次的解决方案

这类方法的主要思想就是通过修改源码,编写出能够防御侧信道的代码实现。这里的核心思想就是隐藏控制流和数据流。

这类方法的探索已经在一些密码算法中有所涉及。比如利用exponentblinding [15] 来增强RSA 算法,利用bit slicing 增强DES 和AES方法[3, 20]。在机器学习领域,也有人做了尝试。Oblivious ML文章[22]修改了机器学习的算法,使用oblivious assignments and comparisons来隐藏控制流,使用oblivious array access(即k-anonymity)来隐藏数据流。文章Raccoon [24] 也采用了类似的方法,使用oblivious store 隐藏if-else 控制流,使用ORAM 来隐藏数据流,从而抵御侧信道攻击。但是目前这些技术还很难在一个通用的计算环境下实现,比如loop trip count,long jump 以及break 等问题。

4.2 系统层次的解决方案

系统层次的解决方案主要是利用一些系统特性来防御或检测SGX 侧信道。这里有几个思路可以参考:

1. 随机化技术(Randomization)。随机化技术可以应用在控制流和数据流上面,这将大大增加侧信道攻击的代价。防御效果与随机化粒度,以及随机化频率有关。

2. 检测可疑异常和中断。T-SGX [26] 利用TSX 技术来检测中断和缺页异常,从而抵御最原始的controlled-channel 攻击[29]。但是现在已经出现不需要触发AEX 的侧信道攻击。

3. 检测时间异常。目前Déjá Vu 系统[4] 也使用TSX 技术来保护enclave自己的时钟。如果攻击者中断或减缓enclave 的运行,enclave就可以通过自己的时钟检测出时间上的异常。目前,绝大多数侧信道攻击都会引起enclave 的显著性能下降。因此,检测时间异常还是一个比较有效的方案。

4. Cache 隔离。目前Intel 推出了CAT(Cache Allocation Technology)技术,允许对cache 进行粗粒度的隔离。这个技术已经被使用在云计算平台上面[18] 防御侧信道攻击,但是还没有看到在SGX 环境里面的应用。把CAT 应用到SGX 的一个很大的障碍是enclave在用户空间无法有效地检测或验证CAT 的配置。

4.3 硬件层次的解决方案

硬件层次的解决方案还处于探索阶段。加?侧信道防御,将会显著增加硬件复杂度,影响功耗和性能。这也可能是Intel 在最初推出SGX 的时候没有加入侧信道防御的一个原因。硬件解决方案可能有以下两种:

1. 硬件分割(partition)。类似于ARM里面的trustzone,有自己的cache,memory 等一系列硬件资源,物理上与non-enclave 分离。

2. 硬件隔离(isolation)。类似于Intel CAT 技术,可以单独为每一个enclave 提供一个动态隔离出的cache。当enclave 销毁的时候,隔离出的cache 可以被收回。这??个很重要的要求就是enclave 必须可以验证这个功能的有效性。

Sanctum [7] 已经做了一些尝试,但是还不够彻底,还会遭受攻击[1]。

5 总结

本文总结了SGX 所面临的侧信道攻击,并展望了潜在的攻击和防御方法。SGX 的侧信道攻击十分难以防御。究其原因是SGX 的安全假设和应用模型允许enclave 和不可信的non-enclave 共享大量的资源。这些就给攻击者以很大的攻击面去区分时间上的差异和资源使用的不同,从而泄露enclave 的控制流和数据流。而且攻击者拥有管理系统资源的能力,从而能够最大程度上减小噪音干扰,增加侧信道攻击的成功率。总之,SGX 侧信道攻击是一个实用的攻击,我们在实际部署应用SGX 的时候,必须考虑潜在的侧信道攻击。

参考文献

[1] Software grand exposure: Sgx cache attacks are practical.In 11th USENIX Workshop on Offensive Technologies (WOOT17), Vancouver, BC, 2017. USENIX Association.

[2] LZMA Benchmark. Intel skylake benchmark.

[3] Eli Biham. A fast new des implementation in software. In FSE,volume 1267, pages 260–272. Springer, 1997.

[4] Sanchuan Chen, Xiaokuan Zhang, Michael K Reiter, and YinqianZhang. Detecting privileged side-channel attacks inshielded execution with déjá vu. In Proceedings of the 2017ACM on Asia Conference on Computer and CommunicationsSecurity, pages 7–18. ACM, 2017.

[5] Xiaoxin Chen, Tal Garfinkel, E. Christopher Lewis, PratapSubrahmanyam, Carl A. Waldspurger, Dan Boneh, JeffreyDwoskin, and Dan R.K. Ports. Overshadow: A virtualizationbasedapproach to retrofitting protection in commodity operatingsystems. In Proceedings of the 13th InternationalConference on Architectural Support for Programming Languagesand Operating Systems, ASPLOS XIII, pages 2–13,New York, NY, USA, 2008. ACM.

[6] Yueqiang Cheng, Xuhua Ding, and Robert H. Deng. Efficientvirtualization-based application protection against untrustedoperating system. In Proceedings of the 10th ACM Symposiumon Information, Computer and Communications Security,ASIA CCS ’15, pages 345–356, New York, NY, USA,2015. ACM.

[7] Victor Costan, Ilia Lebedev, and Srinivas Devadas. Sanctum:Minimal hardware extensions for strong software isolation.In 25th USENIX Security Symposium (USENIX Security 16),pages 857–874, Austin, TX, 2016. USENIX Association.

[8] Johannes G¨otzfried, Moritz Eckert, Sebastian Schinzel, andTilo Müller. Cache attacks on intel sgx. In Proceedings of the10th European Workshop on Systems Security, EuroSec’17,pages 2:1–2:6, New York, NY, USA, 2017. ACM.

[9] Daniel Gruss, Clémentine Maurice, Anders Fogh, Moritz Lipp,and Stefan Mangard. Prefetch side-channel attacks: Bypassingsmap and kernel aslr. In Proceedings of the 2016 ACMSIGSAC Conference on Computer and Communications Security,CCS ’16, pages 368–379, New York, NY, USA, 2016.ACM.

[10] Daniel Gruss, Clémentine Maurice, Klaus Wagner, and StefanMangard. Flush+flush: A fast and stealthy cache attack. In13th Conference on Detection of Intrusions and Malware &Vulnerability Assessment (DIMVA), 2016.

[11] Daniel Gruss, Raphael Spreitzer, and Stefan Mangard. Cachetemplate attacks: Automating attacks on inclusive last-levelcaches. In Proceedings of the 24th USENIX Conference on SecuritySymposium, SEC’15, pages 897–912, Berkeley, CA,USA, 2015. USENIX Association.

[12] Owen S. Hofmann, Sangman Kim, Alan M. Dunn, Michael Z.Lee, and Emmett Witchel. Inktag: Secure applications on anuntrusted operating system. In Proceedings of the EighteenthInternational Conference on Architectural Support for ProgrammingLanguages and Operating Systems, ASPLOS ’13,pages 265–278, New York, NY, USA, 2013. ACM.

[13] Intel. Intel 64 and ia-32 architectures optimization referencemanual. June 2016.

[14] Intel. Intel 64 and IA-32 architectures software developer’smanual combined volumes: 1, 2a, 2b, 2c, 2d, 3a, 3b, 3c, 3dand 4. March 2017.

[15] Paul C. Kocher. Timing attacks on implementations of diffiehellman,rsa, dss, and other systems. In Proceedings ofthe 16th Annual International Cryptology Conference on Advancesin Cryptology, CRYPTO ’96, pages 104–113, London,UK, UK, 1996. Springer-Verlag.

[16] Sangho Lee, Ming-Wei Shih, Prasun Gera, Taesoo Kim, HyesoonKim, and Marcus Peinado. Inferring fine-grained controlflow inside SGX enclaves with branch shadowing. CoRR,abs/1611.06952, 2016.

[17] Moritz Lipp, Daniel Gruss, Raphael Spreitzer, Clémentine Maurice,and Stefan Mangard. Armageddon: Cache attacks onmobile devices. In 25th USENIX Security Symposium (USENIXSecurity 16), pages 549–564, Austin, TX, 2016. USENIX Association.

[18] Fangfei Liu, Qian Ge, Yuval Yarom, Frank McKeen, Carlos V.Rozas, Gernot Heiser, and Ruby B. Lee. Catalyst: Defeatinglast-level cache side channel attacks in cloud computing.2016 IEEE International Symposium on High PerformanceComputer Architecture (HPCA), pages 406–418, 2016.

[19] Fangfei Liu, Yuval Yarom, Qian Ge, Gernot Heiser, and Ruby B.Lee. Last-level cache side-channel attacks are practical. InProceedings of the 2015 IEEE Symposium on Security and Privacy,SP ’15, pages 605–622, Washington, DC, USA, 2015.IEEE Computer Society.

[20] Mitsuru Matsui. How far can we go on the x64 processors?In FSE, volume 4047, pages 341–358. Springer, 2006.

[21] Ahmad Moghimi, Gorka Irazoqui, and Thomas Eisenbarth.Cachezoom: How SGX amplifies the power of cache attacks.CoRR, abs/1703.06986, 2017.

[22] Olga Ohrimenko, Felix Schuster, Cedric Fournet, AasthaMehta, Sebastian Nowozin, Kapil Vaswani, and Manuel Costa.Oblivious multi-party machine learning on trusted processors.In 25th USENIX Security Symposium (USENIX Security 16),pages 619–636, Austin, TX, 2016. USENIX Association.

[23] Peter Pessl, Daniel Gruss, Clémentine Maurice, MichaelSchwarz, and Stefan Mangard. Drama: Exploiting dram ad-dressing for cross-cpu attacks. In 25th USENIX Security Symposium,2016.

[24] Ashay Rane, Calvin Lin, and Mohit Tiwari. Raccoon: Closingdigital side-channels through obfuscated execution. In 24thUSENIX Security Symposium (USENIX Security 15), pages431–446, Washington, D.C., 2015. USENIX Association.

[25] Michael Schwarz, Samuel Weiser, Daniel Gruss, ClémentineMaurice, and Stefan Mangard. Malware guard extension: UsingSGX to conceal cache attacks. CoRR, abs/1702.08719,2017.

[26] Ming-Wei Shih, Sangho Lee, Taesoo Kim, and Marcus Peinado.T-sgx: Eradicating controlled-channel attacks against enclaveprograms. In Proceedings of the 2017 Annual Network andDistributed System Security Symposium (NDSS), San Diego,CA, 2017.

[27] Shweta Shinde, Zheng Leong Chua, Viswesh Narayanan, andPrateek Saxena. Preventing page faults from telling your secrets.In Proceedings of the 11th ACM on Asia Conferenceon Computer and Communications Security, ASIA CCS ’16,pages 317–328, New York, NY, USA, 2016. ACM.

[28] Wenhao Wang, Guoxing Chen, Xiaorui Pan, Yinqian Zhang,XiaoFeng Wang, Vincent Bindschaedler, Haixu Tang, andCarl A. Gunter. Leaky cauldron on the dark land: Understandingmemory side-channel hazards in SGX. CoRR,abs/1705.07289, 2017.

[29] Yuanzhong Xu, Weidong Cui, and Marcus Peinado. Controlledchannelattacks: Deterministic side channels for untrusted operatingsystems. In Proceedings of the 2015 IEEE Symposiumon Security and Privacy, SP ’15, pages 640–656, Washington,DC, USA, 2015. IEEE Computer Society.

[30] Yuval Yarom and Katrina Falkner. Flush+reload: A high resolution,low noise, l3 cache side-channel attack. In Proceedingsof the 23rd USENIX Conference on Security Symposium,SEC’14, pages 719–732, Berkeley, CA, USA, 2014. USENIXAssociation.

本文分享自微信公众号 - 百度安全实验室(BaiduX_lab)。

如有侵权,请联系 support@oschina.cn 删除。

本文参与“OSC源创计划”,欢迎正在阅读的你也加入,一起分享。