计算机组成

7 流水线处理器

7.3 超标量流水线

超标量流水线在现代的处理器当中得到了广泛的应用,也就是这种技术给我们带来了出色的处理器性能。那究竟什么才是超标量流水线,它又是如何工作的呢?我们这一节将一起探讨这个问题。

这个是我们之前已经构建好的一条流水线,但是如果我们觉得它的吞吐率还不够高。其中一个改进的方向就是加深流水线,而与之相对另一个改进的方向就是拓宽流水线。而拓宽流水线的这个方案我们就称为超标量。在现在通常来说超标量的结构是只有两条或者有两条以上可以并行工作的流水线,那好就这个厨房的例子,现在为了满足更多客人的需求,我们就需要把这条做菜的流水线进行拓宽。我们从左往右来看首先我把这个洗菜的池子扩大一倍,这样就可以同时洗两道菜的原料了。那与之相匹配的后面的各个环节都得加倍,这样我们就有了两条可以并行工作的流水线,这就是一条超标量流水线。在处理器设计当中我们也经常简称为超标量。那么与超标量流水线相对,以前的单条流水线就可以被称为标量流水线,那采用了超标量结构的处理器,我们也常称之为超标量处理器。

那么就结合这个例子简单的来看一看超标量流水线是如何工作的。既然我们这个洗菜的池子扩大了一倍,那么同时就可以进行两道菜的操作,那么当一分钟过去之后。

洗菜这个环节就会将这两份菜的原料分别送到切菜1这个环节的两位操作人员手中,而与此同时第三道菜和第四道菜则会进入洗菜环节。

这样在每一个环节都有两道菜菜在同时的并行向前。那到了五分钟的时候就可以同时完成两道菜。而对于处理器,这也常被称为双发射的结构。那如果照着这个方式再扩展一条流水线就变成三发射,再扩大一条就会变成四发射,这就是超标量流水线的基本工作原理。

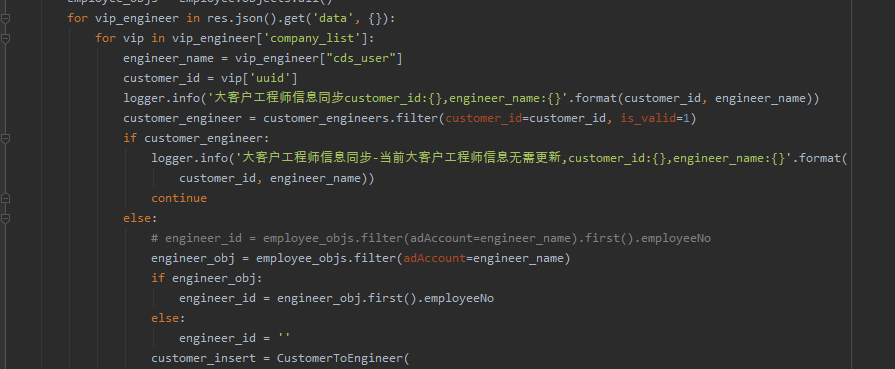

那我们再来看一些实际的例子。奔腾是第一款采用超标量技术的x86CPU。这就是奔腾的流水线结构,它是一个双发射的五级流水线,这两条流水线分别被命名为U流水和V流水。它们共用取指和译码的部件,但是有自己独立的地址生成逻辑,ALU 以及数据高速缓存的接口。那在一个时钟周期内可以同时发送两条指令,分别到U流水和V流水。当然超标量技术并不是到这个时候才诞生的,而是在很多年前就在计算机当中获得了应用。

这是历史上第一台超级计算机CDC6600。那么在这台计算机当中,有十个并行的功能部件,因此也被认为是最早采用了超标量技术的计算机。不过这些功能部件内部并没有采用流水线,所以从这里我们可以看出超标量技术和流水线技术实际上是相互独立的,只不过在现在采用了超标量技术的CPU也都是使用流水线的技术。

虽然CDC6600没有采用流水线,但它的下一代产品CDC7600就在这些并行的功能部件内实现了流水线的技术。

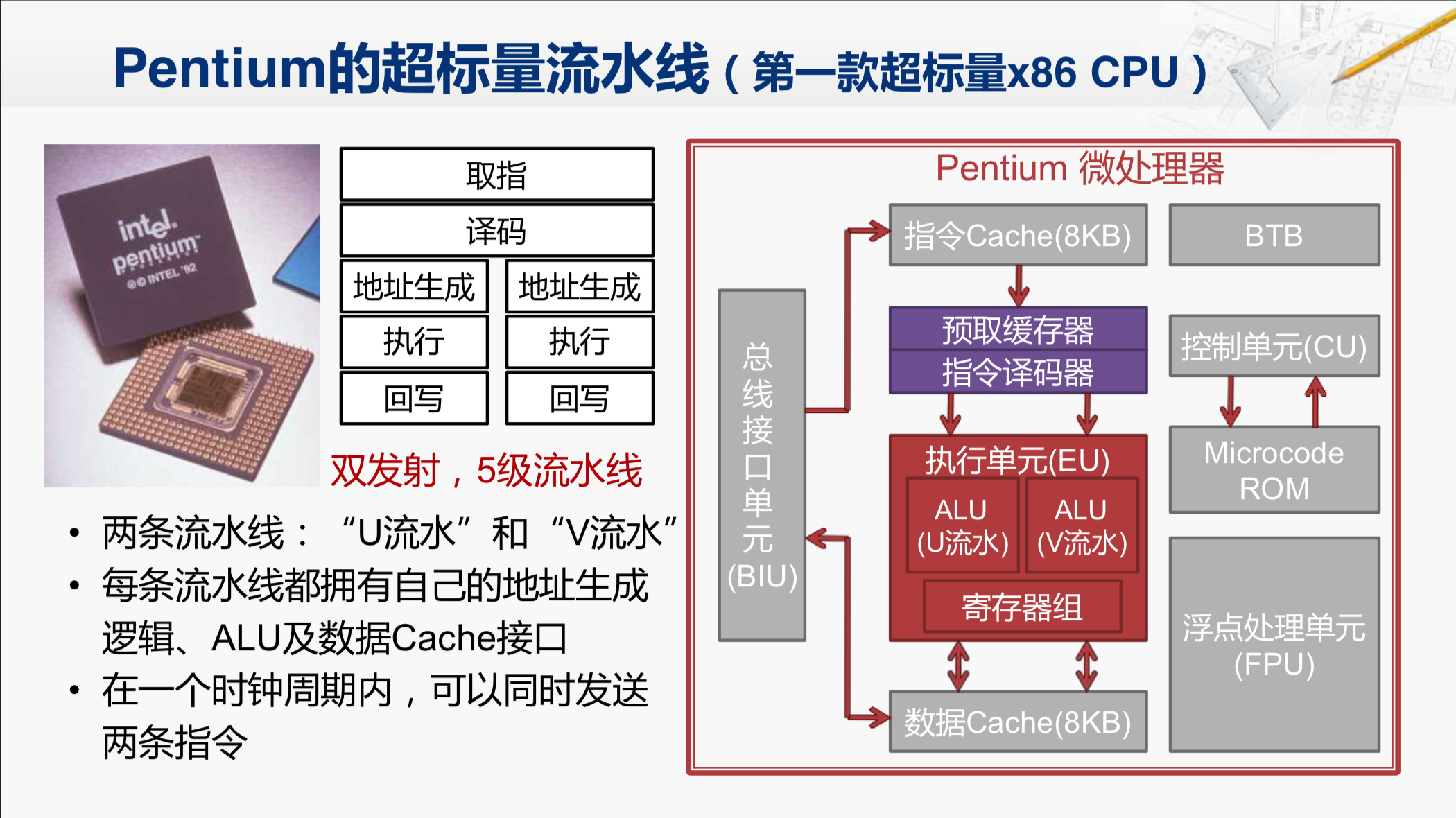

那我们再回到现在,ARM Cortex-A9的流水线结构。它每个时钟周期可以发射四条指令,根据指令的不同,总共会经过八到十一级流水线。与奔腾类似的是在流水线的前端比如说取指,译码并没有分成多条流水线而是采用统一的部件。当然我们要知道这些部件虽然看上去是一个,但它实际上比标量流水线要大得多。比如说取指部件至少一次要能取来四条指令甚至更多,而译码部件一次也至少应该完成四条指令的译码。而到了流水线的后端,才会从结构表示上体现出多条并行流水线的形态。

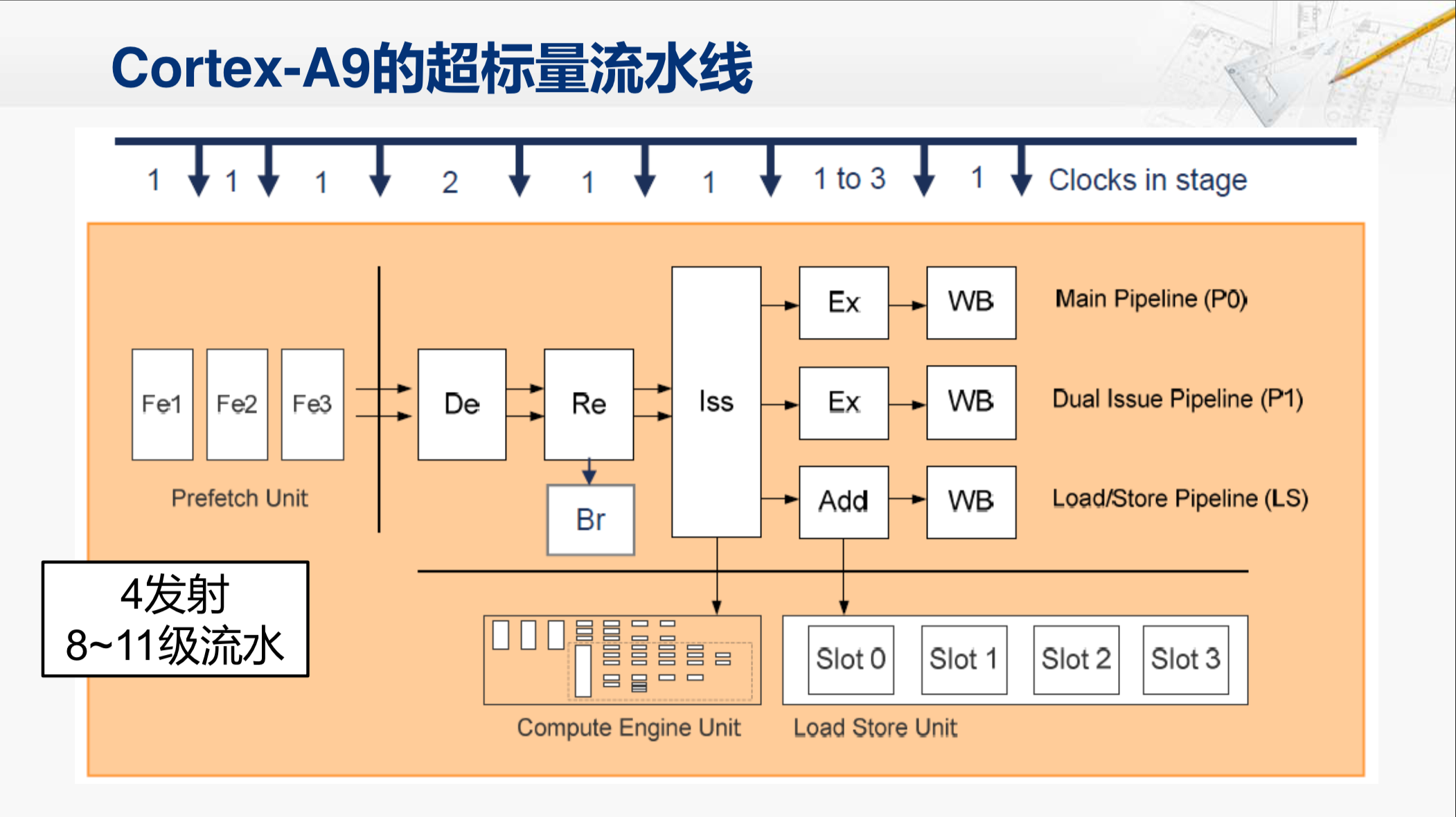

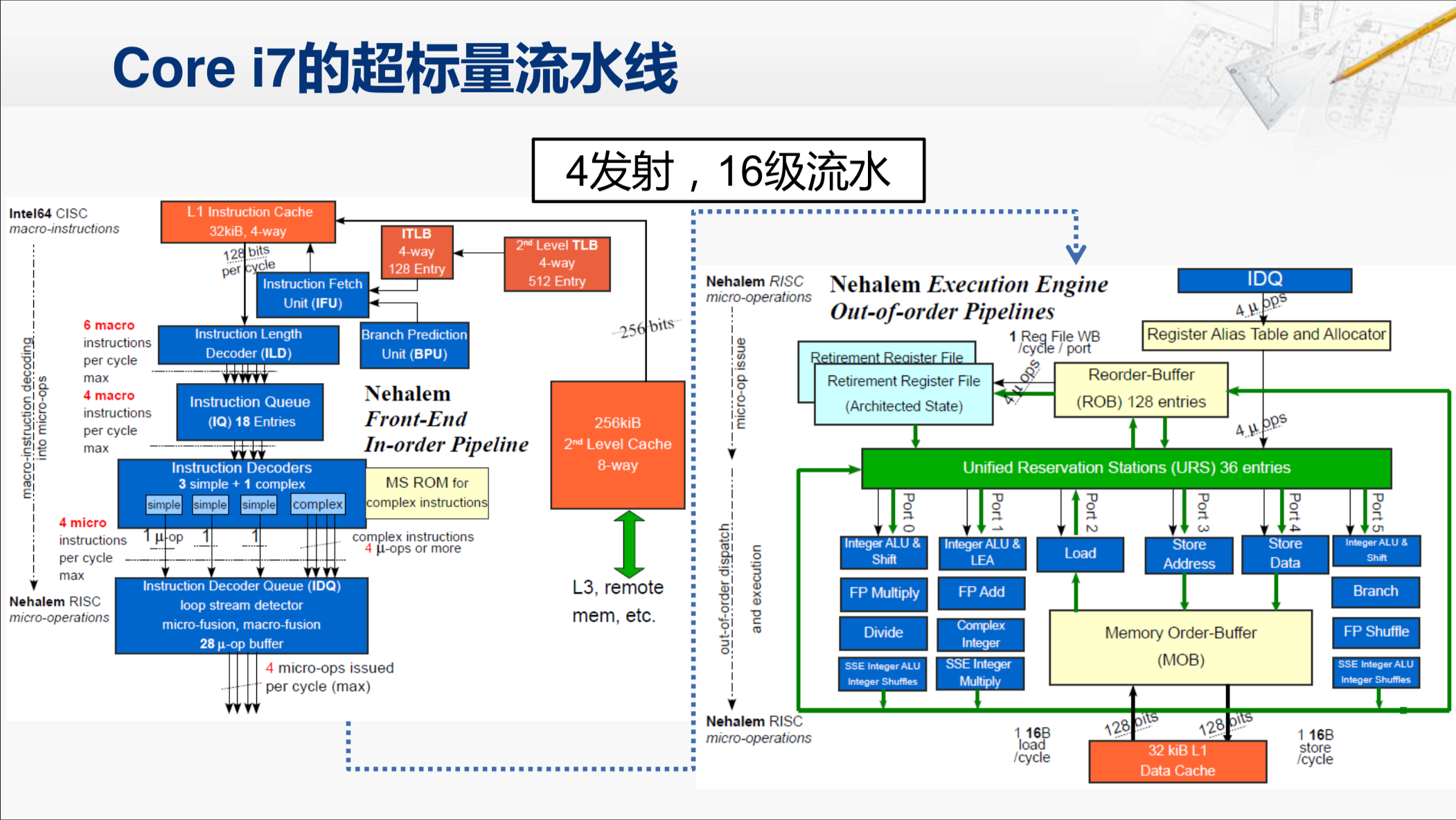

然后我们再来看Core i7的超标量流水线。这个流水线就更为复杂,这个是指令高度缓存(L1 Instruction Cache)也就相当于我们在流水线原理当中提到的指令存储器。我们可以看到每个周期从指令存储器当中会取回128个比特,也就是十六个字节,因为x86指令长度是不固定的,所以首先要经过一个指令长度的译码器(ILD),分解出到底哪几个字节是一条指令。那么在这一点上MIPS指令系统就体现出了明显的优势,它每条指令都是定长的,不用额外进行这样的识别工作。那么还有一点值得一提的是在译码器当中通过硬件会将x86的指令转换成更为简单的指令,这些指令被称为微操作,那从这里(Instruction Decoders)可以看出有三个简单的译码器(simple),用于对那些比较简单的x86指令进行转换,每条指令对应一个微操作。而那些非常复杂的指令则会通过这个复杂的译码器(complex)转换成多条微操作,而这些微操作都是类似于RISK指令的格式,这样在它流水器的后半部分看到的都是RISK格式的简单指令了。那这张图(左半部分)还只是流水线的前半部分。

我们再画出后半部分(右半部分)。在这里我们也可以看出多条并行的流水线(Port 0~5),而且因为在这个流水线当中运行的是微操作,都是采用了RISK的编码风格。所以,这里也可以充分运用大量面向RISK处理器研发出的高级流水线的技术。这也就是为什么我们现在经常说x86虽然是一个CISK的指令系统,但它实际上是用RISK的方式去实现的。

那这个CPU就是一个4发射16级流水的超标量流水线。

那我们再来比较一下超标量流水线和之前的标量流水线。最开始从单周期处理器到流水线处理器主要考虑的是时间并行性上的优化,通过_对现有硬件进行切分_,只是增加了少量的流水线寄存器以及部分的控制信号的改动,那原本串行执行的指令在一定程度上并行起来。而从标量流水线到超标量流水线则是主要考虑了空间并行性上的优化,这是让_不同的指令同时在不同的流水线上运行_,那么简单的看来每增加一个发射数就需要增加一条流水线的硬件资源。

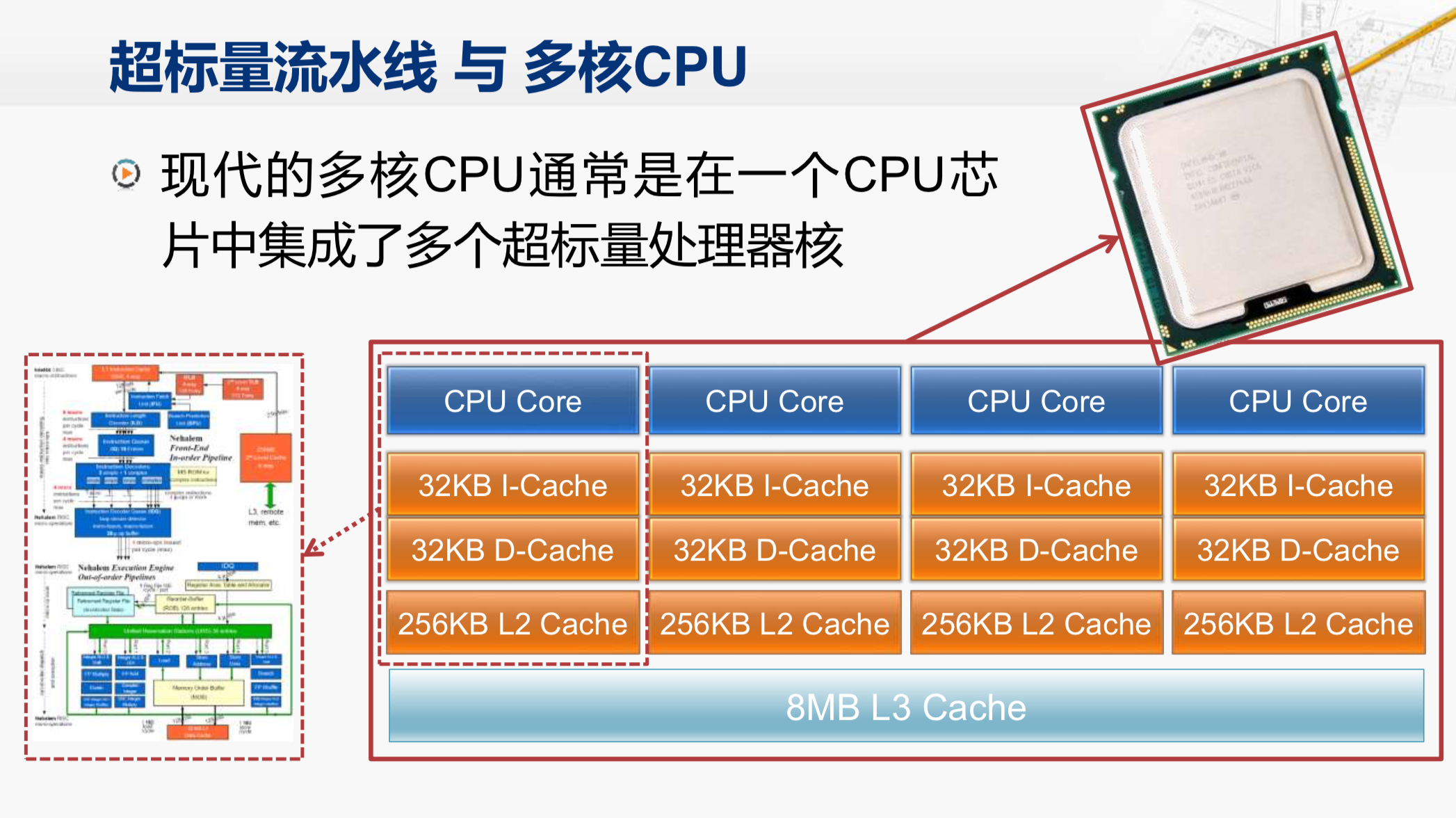

我们最后来看一看超标量流水线与多核的关系。从原理上讲它们都是在空间并行性方面寻求的优化,我们还是看一个实际的例子。这就是Core i7,也是我们现在熟知的多核超标量处理器。那么来看看它内部的结构。

首先我们来看一个概念叫做处理器核。这部分实际上就包含了我们之前介绍的那些数据通路控制信号等等。当然还需要包含指令和数据的高度缓存(I-Cache和D-Cache),对应了我们原理结构当中的指令存储器(Instruction Memory)和数据存储器(Data Memory)。那为了提高性能现在的处理器当中一般还配备了二级的高速缓存(L2 Cache)。这些部件的关系非常紧密,我们通常也就把这一部分称为一个处理器核。

那么刚才看到那个4发射16级流水线的结构图就是在只这么一个处理器核内部的结构(图中最左边虚线内的框图),那么可以说这一个处理器核就是一个超标量流水线的处理器核。而在单核的时代这个部分结构就单独制造出了一个芯片,就是以前的单核CPU。那现在我们把这样同样的结构复制多份,然后再加上一些共享的存储部件就构成了一个多核的CPU,这里面有四个核那就是一个四核的CPU。每一个核内部都是一个超标量流水线的结构,这就是我们现在通常说的多核CPU和超标量流水线之间的关系。

现在我们已经从整体框架层面了解了流水线处理器的发展演变的过程,而且也知道了现代最先进流水线处理器的大体结构。但是仅仅了解这些是不够的,流水线的方式引入处理器之后它自身也带来了一些新的问题,我们必须了解并解决这些问题。这是我们下一节将要探讨的主题。