GPIO原理及配制方法

引用地址:

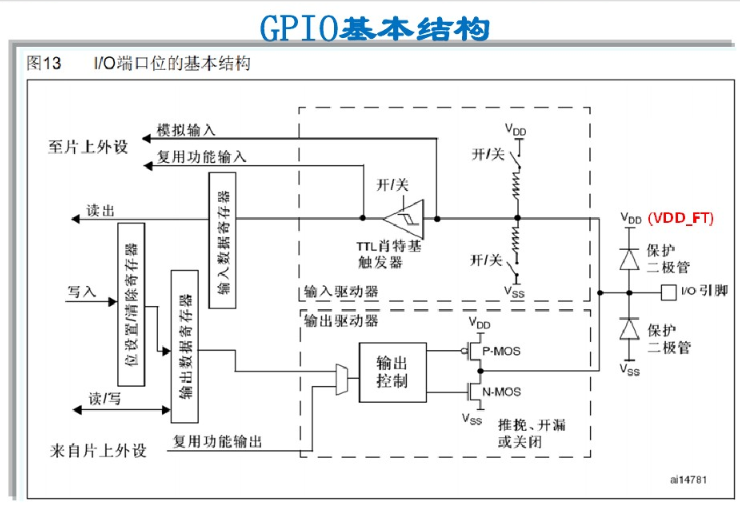

ARM SOC芯片的GPIO结构示意图

@@@

GPIO的八种模式

1,输入浮空模式

2,输入上拉模式

3,输入下拉模式

4,模拟输入模式

5,开漏输出模式

6,开漏复用功能模式

7,推挽输出模式

8,推挽复用功能模式

@@@

三个最大输出速度

---------2MHZ----------

---------10MHZ--------

---------50MHZ--------

@@@

ARM_SOC的GPIO相关寄存器

@——GPxCON寄存器:

从寄存器的名字可以看出,它用于配置(Configure)-选择引脚功能。

@——GPxDAT寄存器:

GPxDAT用于读/写引脚;当引脚被设为输入时,读此寄存器可知相应引脚的电平状态是高还是低;当引脚被设为输出时,写此寄存器相应位可以令此引脚输出高电平或是低电平。

@——GPxUP寄存器:

GPxUP:某位为1时,相应引脚无内部上拉电阻;为0时,相应引脚使用内部上拉电阻。

上拉电阻的作用在于:当GPIO引脚处于第三态(即不是输出高电平,也不是输出低电平,而是呈高阻态,即相当于没接芯片)时,它的电平状态由上拉电阻、下拉电阻确定。

总结一下:单个GPIO管脚的控制是通过软件写相应的寄存器的操作的,根据不同的SOC有的用一个位,也有的用多个位来操作。

@@@@@@@@

访问硬件的方式:

1,单个引脚的操作无外乎3种:输出高低电平、检测引脚状态、中断。对某个引脚的操作一般通过读、写寄存器来完成。

2,以总线方式访问硬件,并非只能通过寄存器才能发出硬件信号,实际上通过访问总线的方式控制硬件更为常见。如下图所示S3C2410/S3C2440与NOR

Flash的连线图,读写操作都是16位为单位。

图中缓冲器的作用是以提搞驱动能力、隔离前后级信号。NOR

Flash(AM29LV800BB)的片选信号使用nGCS0信号,当CPU发出的地址信号处于0x00000000~0x07FFFFFF之间时,nGCS0信号有效(为低电平),于是NOR

Flash被选中。这时,CPU发出的地址信号传到NOR Flash;进行写操作时,nWE信号为低,数据信号从CPU发给NOR

Flash;进行读操作时,nWE信号为高,数据信号从NOR Flash发给CPU。

ADDR1ADDR20 ------------------> >--------------------A0A19

DATA0DATA15 <-----------------> <------------------->D0D15

nOE ------------------> -------------------->nOE

nWE ------------------> -------------------->nWE

nGCS0 ------------------> -------------------->nCE

S3C2410/S3C2440 缓冲器 NOR Flash(AM29LV800BB)

软件如何发起写操作呢,下面有几个例子的代码进行讲解。

1)地址对齐的16位读操作

unsigned short *pwAddr = (unsigned short *)0x2;

unsigned short uwVal;

uwVal = *pwAddr;

上述代码会向NOR Flash发起读操作:CPU发出的读地址为0x2,则地址总线ADDR1ADDR20、A0A19的信号都是1、0...、0(CPU的ADDR0 为0,不过ADDR0没有接到NOR Flash上)。NOR Flash的地址就是0x1,NOR Flash在稍后的时间里将地址上的16位数据取出,并通过数据总线D0~D15发给CPU。

2)地址位不对齐的16位读操作

unsigned short *pwAddr = (unsigned short *)0x1;

unsigned short uwVal;

uwVal = *pwAddr;

由于地址是0x1,不是2对齐的,但是BANK0的位宽被设为16,这将导致异常。我们可以设置异常处理函数来处理这种情况。在异常处理函数中,使用 0x0、0x2发起两次读操作,然后将两个结果组合起来:使用地址0x0的两字节数据D0、D1;再使用地址0x02读到D2、D3;最后,D1、D2组合成一个16位的数字返回给wVal。如果没有地址不对齐的异常处理函数,那么上述代码将会出错。如果某个BANK的位宽被设为n,访问此BANK时,在总线上永远只会看到地址对齐的n位操作。