SDRAM对自己来说是个新东西,所以读起来并不轻松。

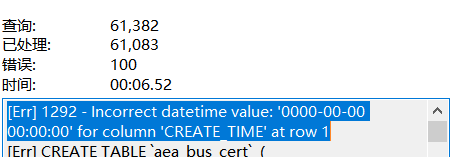

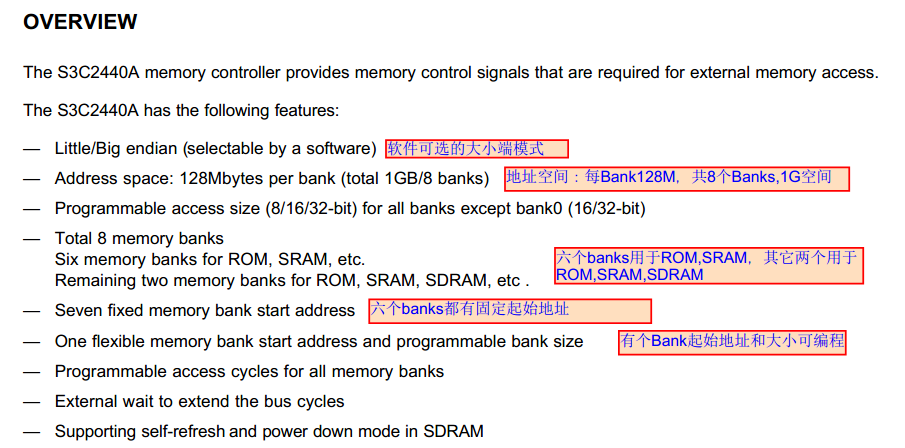

这个RAM的分类有SRAM和DRAM,分别是静态RAM和动态RAM,两个的内部构造不一样,可以百度一下。而SDRAM则是同步的动态RAM,同步的好处就是与处理器控制匹配,操作起来就容易多。下面看看S3C2440的内存控制是怎么样的,下面截图是一个概述。

S3C2440的内存图根据是否由NAND FLASH来启动有不同区别,下图展示了2440复位后的内存分布图。这里有个疑问,看见说可以NOR FLASH启动,还有SDRAM中运行程序,那么这两个是属于那部分呢?以后深入再说吧。

从图可以看出启动不同时Boot Internal位置是不同的。

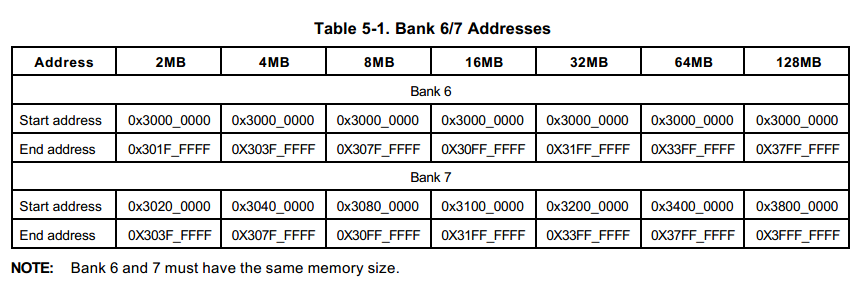

前文说到有个bank可以灵活的配置,这个bank就是bank7,它的配置是依据bank6来进行的。下图进行了说明:

bank0的数据线宽度是固定的16位或24位。因为bank0(内存地址中的0x0000_0000)用作启动区,所以在上电之前就要确定它的数据线宽度。

宽度有两个引脚OM[0:1]的电平决定。

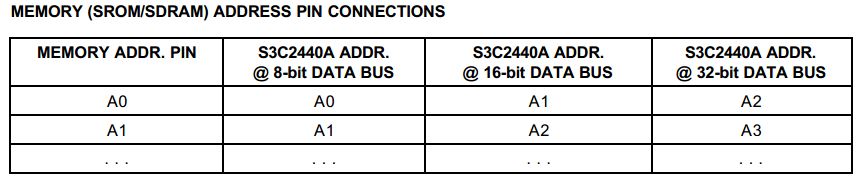

CPU的地址线与外围SRAM,SDRAM内存地址线的连接也是有讲究注意的。分别是8位、16位和32位。下图说明:

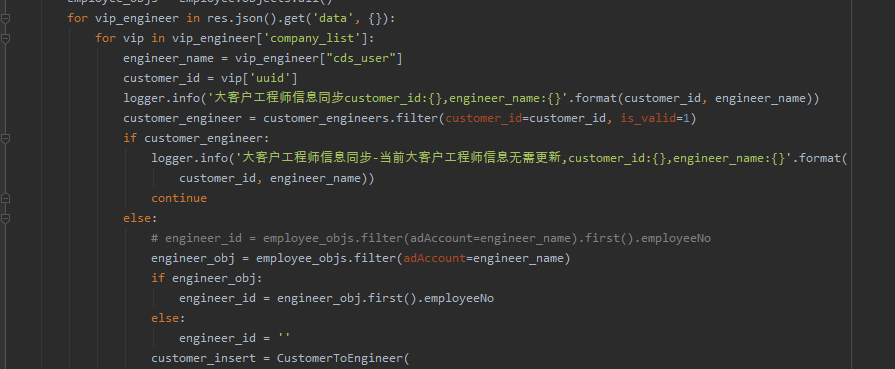

这里为什么8位就从A0开始,而其它的就从因为A1,A2分别开始。是这个原因,以16位进行说明。首先CPU寻址空间,字节为存储容量的基本单位。一个16位数据线的SDRAM,可以认为它的存储基本单位是2个字节。这样对于16位SDRAM,A0:A1=01时,对应2440的A2:A1=01.A0好像就是2个字节的基数这个意思,可以省略掉。我的板子是用到了两片16位SDRAM构成32位,所以连接方式是最后一种。下面的截图是我的原理图中SDRAM的连接方法。

其中BA0与BA1与ADD24和ADD25相连,代表SDRAM最高地址位。因为两个32M的SDRAM合并成64M空间,那么按照计算就需要26根数据线。13根行地址线与9根列地址线=22根,加上这个SDRAM的存储单元是2个字节,就又相当于多了一根地址线,最后BA0,BA1为最高地址位。合起来就可以寻址64M了。

跟内存控制的寄存器BWSCON,BANKCONx(x=05),BANKCONx(x=67),REFRESH,BANKSIZE,MRSRBx(x=6~7).下面分别简要说明。

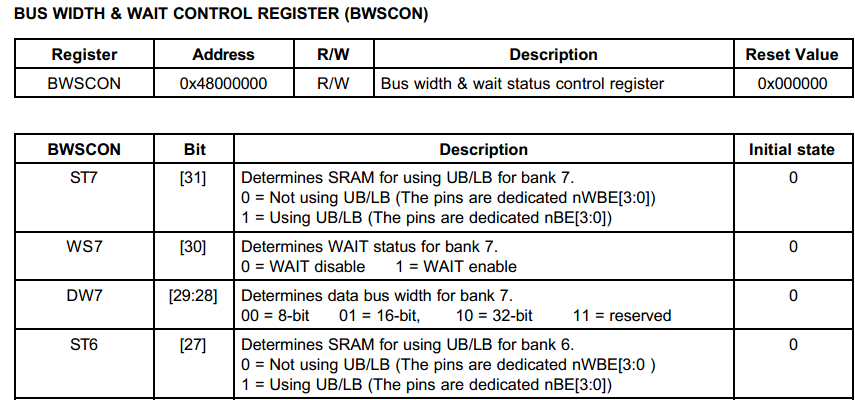

BWSCON(位宽和等待控制寄存器):

这个寄存器设定各个存储块数据宽度和WAIT使能。截图一部分看看其中含义吧。

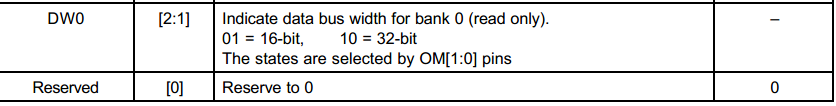

其中每四位控制一个BANK,注意的是BANK0因为是启动区有些特殊。截图如下:

DW只读,有前文讲到的OM引脚决定。

BANKCONx(x=0~5)(BANK控制寄存器):

该寄存器控制一些跟SDRAM的相关的时间参数。截图如下:

01位PMC跟页模式有关,暂时不知道干什么用的。(跟MMU有关?)

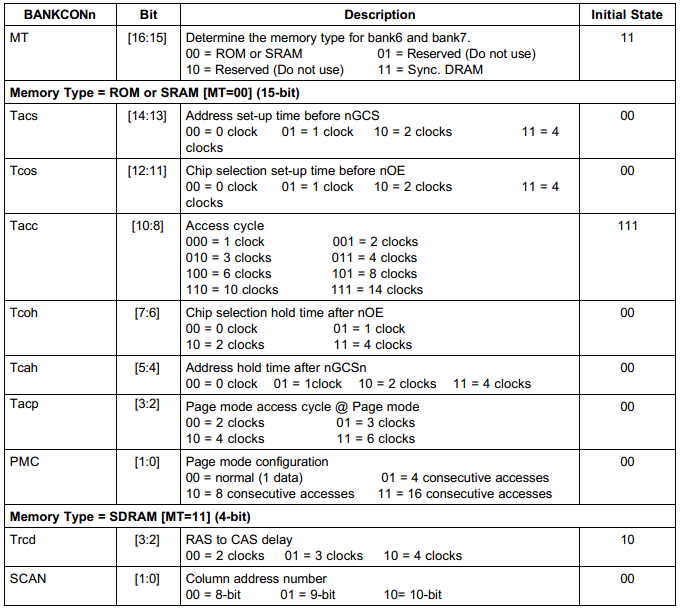

BANKCONx(x=6~7)(BAMK控制寄存器)

因为设计到可以控制SDRAM,所以BANK6/7与前面5个不太一样。

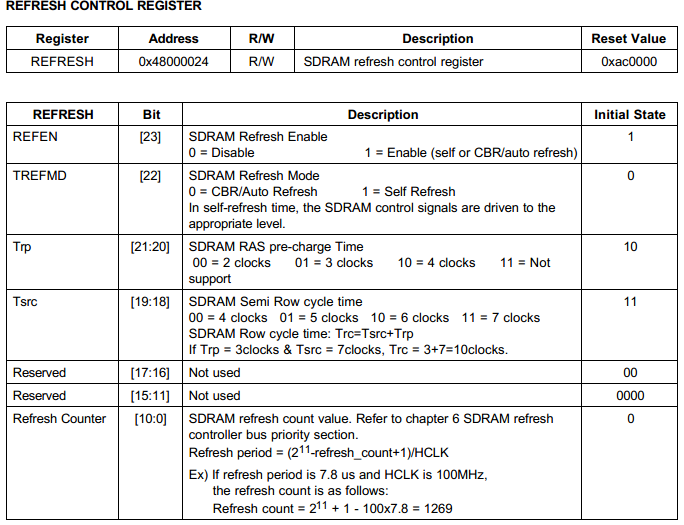

REFRESH刷新控制寄存器

这个寄存器的存在是为SDRAM服务的,因为DRAM的特性决定了它需要不停的刷新来保存数据。

SDRAM行周期时间公式为Trc = Tsrc + Trp

刷新时间公式为上图也有说明:刷新时间=(2^11-刷新计数值+1)/HCLK。比如我们使用的SDRAM刷新周期=64ms/8192=7.8125us,HCLK=199MHz时,刷新计数值 = 2^11 - 100x7.8+1=1269。16进制为0x4F5,则上图寄存器中0到10位的Refresh Counter值为0x4F5.

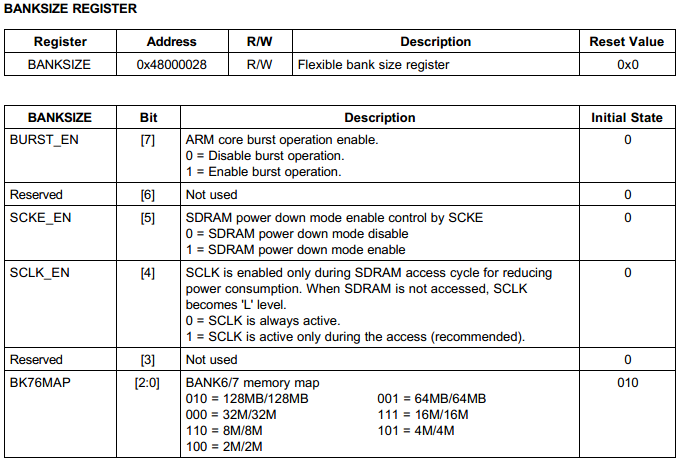

BANKSIZE存储块大小控制器

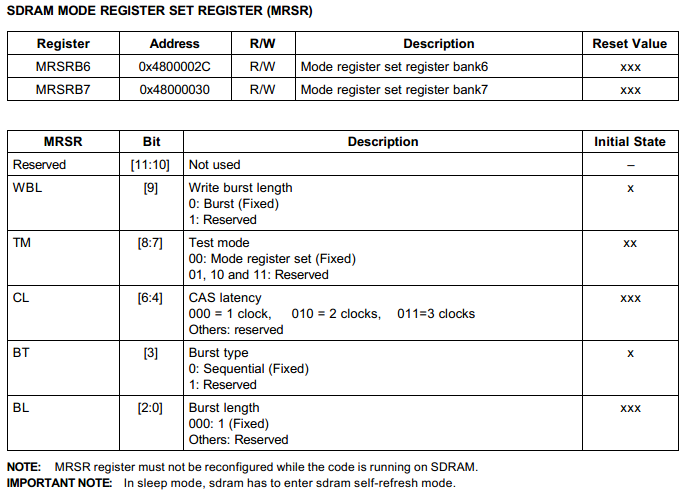

MRSRBx(x=6~7)SDRAM模式设置寄存器

这个主要是跟SDRAM有关。

只有CL[6:4]可以修改。其它都是固定的。

上面的寄存器就是涉及到内存管理的一些重要寄存器。

因为我的机子配置的是两块SDRAM,共64M。所以主要的操作设计到SDRAM,而不是SRAM。

其实还是对内存控制这里还是有很多不懂,只有以后随着学习继续理解了。 未完待续。。。

未完待续。。。